## Ph.D. DISSERTATION

## Simplifying Reasoning under Weak Memory Concurrency

느슨한 메모리 프로그램을 쉽게 이해하기

August 2023

# DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

Minki Cho

## Simplifying Reasoning under Weak Memory Concurrency

느슨한 메모리 프로그램을 쉽게 이해하기

지도교수 허충길 이 논문을 공학박사 학위논문으로 제출함 2023년 7월

> 서울대학교 대학원 컴퓨터공학부 조 민 기

조민기의 공학박사 학위논문을 인준함 2023년 7월

| 위 원         |   | 이 광 근     | afatt.    |

|-------------|---|-----------|-----------|

| 부위원장        |   | 허 충 길     | ( Cold )  |

| 위           | 원 | Ori Lahav | 12/ ([8]) |

| 위<br>위<br>위 | 원 | 강 지 훈     | 12278     |

| 위           | 원 | 김 지 응     | ASIB      |

Abstract

This thesis presents ways to easily implement concurrent programs in weak memory.

In shared memory concurrency, programs have counterintuitive (or weak) behavior

due to hardware and compiler optimizations. It is difficult to implement a correct

program with a full understanding of weak behavior. I develop two theories that

simplify reasoning under weak memory concurrency. First, I formalize and prove local

data-race-freedom guarantees that ensure strong semantics for locations accessed by

non-racy instructions. These allow programmers who avoid data races to understand

and write concurrent programs without understanding of weak behavior. Next, I

show that sequential reasoning is adequate and sufficient for establishing soundness of

compiler optimizations under weak memory. I introduce a sequential model SEQ which

has no weak behavior and no concurrency, and show that correct optimizations under

SEQ executions are also correct under weak memory. Our results are fully verified

against a weak memory model, the promising semantics.

**Keywords:** Relaxed Memory Concurrency, Operational Semantics, Data Race Free-

dom, Compiler Optimization, Verified Compilation

**Student Number**: 2017-29003

i

## Contents

| Abstra | ct      |                                                            | i  |

|--------|---------|------------------------------------------------------------|----|

| Chapte | er 1 P  | rologue                                                    | 1  |

| 1.1    | Introd  | $\operatorname{uction} \ldots \ldots \ldots \ldots \ldots$ | 1  |

| 1.2    | Backgr  | cound: The Promising Semantics                             | 2  |

|        | 1.2.1   | The Promising Semantics                                    | 2  |

|        | 1.2.2   | Additional Examples of the Promising Semantics             | 9  |

| Chapte | er 2 L  | ocal Data-Race-Freedom Guarantees for Program Writers      | 11 |

| 2.1    | Introd  | uction: The Need for Local DRF                             | 11 |

| 2.2    | Local   | DRF in Weak Memory Models                                  | 16 |

|        | 2.2.1   | Local DRF w.r.t. an "In-Order" Semantics                   | 16 |

|        | 2.2.2   | Local DRF w.r.t. RA and SC                                 | 22 |

| 2.3    | Local 1 | DRF Guarantees                                             | 25 |

|        | 2.3.1   | Local DRF-PF                                               | 26 |

|        | 2.3.2   | Local DRF-RA                                               | 29 |

|        | 2.3.3   | Local DRF-SC                                               | 31 |

|        | 2.3.4   | Time-wise Local DRF Guarantees                             | 33 |

| 2.4    | Applyi  | ing LDRF for Modular Reasoning                             | 35 |

|                | 2.4.1 Reasoning About Client Code              | 36        |  |  |  |  |  |

|----------------|------------------------------------------------|-----------|--|--|--|--|--|

|                | 2.4.2 Reasoning About Library Code             | 39        |  |  |  |  |  |

| 2.5            | Mapping PS2.1 to Hardware                      | 40        |  |  |  |  |  |

| 2.6            | A Counterexample to Local DRF in PS            | 43        |  |  |  |  |  |

| 2.7            | Conclusion and Related Work                    |           |  |  |  |  |  |

| Chapte         | er 3 Sequential Reasoning for Compiler Writers | <b>50</b> |  |  |  |  |  |

| 3.1            | Introduction: Optimizations under Weak Memory  | 50        |  |  |  |  |  |

| 3.2            | The Sequential Permission Machine              | 55        |  |  |  |  |  |

| 3.3            | Advanced Behavior Refinement                   | 66        |  |  |  |  |  |

| 3.4            | An Overview of a Certified Optimizer           | 72        |  |  |  |  |  |

| 3.5            | A Certified Optimizer in Detail                | 75        |  |  |  |  |  |

|                | 3.5.1 Optimizations in Detail                  | 75        |  |  |  |  |  |

|                | 3.5.2 Simulation Relation in SEQ               | 78        |  |  |  |  |  |

| 3.6            | Non-atomics in the Promising Semantics         | 79        |  |  |  |  |  |

| 3.7            | Adequacy of Sequential Reasoning               | 84        |  |  |  |  |  |

| 3.8            | Conclusion and Related Work                    | 87        |  |  |  |  |  |

| Bibliography 9 |                                                |           |  |  |  |  |  |

| 초록             |                                                | 101       |  |  |  |  |  |

| 감사의            | 글                                              | 102       |  |  |  |  |  |

## Chapter 1

## Prologue

## 1.1 Introduction

Writing and compiling programs correctly under shared memory concurrency is difficult. In shared memory concurrency, programs have counterintuitive (or "weak") behavior due to hardware and compiler optimizations. Weak memory models are introduced to abstract complicated weak behavior and allow programmers to write correct programs without sacrificing optimizations.

However, despite recent advances, weak memory models are too complex. Weak memory models introduce complicated states and out-of-order execution to properly model weak behavior. These complexities dramatically increase the number of cases to consider when reasoning about program execution.

In this thesis, I propose methods to simplify reasoning under weak memory concurrency. The main idea is to provide a simple and understandable model for programmers instead of the full weak memory model. Importantly, reasoning from the simple model can be *lifted* to the full weak memory model. Thanks to this

property, programmers can reason correctly about weak memory programs without understanding weak memory models.

I give two main results. The first result, presented in Chapter 2, is the local data-race-free guarantee for programmers writing programs that run under weak memory concurrency. It guarantees that reasoning under the simple memory models is still sound in the fully weak memory model under certain conditions. This result was published in PLDI'2021 under the title "Modular Data-Race-Freedom Guarantees in the Promising Semantics" [1].

The other result presented in Chapter 3 is for compiler writers. Surprisingly, we show that reasoning under the sequential memory model is sound even under weak memory concurrency. This result was published in PLDI'2022 under the title "Sequential Reasoning for Optimizing Compilers under Weak Memory Concurrency" [2].

The results are formalized and verified against the state-of-the-art weak memory model, the *promising semantics* [3, 4]. The formal explanation and examples of the promising semantics are given in Section 1.2.

## 1.2 Background: The Promising Semantics

## 1.2.1 The Promising Semantics

In this section we provide an introduction to the promising semantics. We include only the necessary parts for keeping our presentation self-contained, and refer the reader to [3, 4] for detailed explanations. Our focus is on the version described in [4, §4.4], which we refer to as PS2.1.<sup>1</sup>

We present the fragment of the model containing: relaxed reads and writes (rlx), strong relaxed writes (srlx), release writes (rel), and acquire reads (acq). Read-

<sup>&</sup>lt;sup>1</sup>Most of the details, however, are identical for the original PS model and for the PS2 model (the only difference has to do with the notion of "capped memory" and reservations).

```

M,P\subseteq \mathsf{Msg} \cup \mathsf{Rsv} \quad \mathsf{memory/promise\ set}

f, t \in \mathsf{Time} \triangleq \mathbb{Q}^+

timestamp

thread-local program state

X, Y, Z, L \in \mathsf{Loc}

location

(f,t] \in \mathsf{Time} \times \mathsf{Time}

timestamp interval

T = \langle \sigma, V, P \rangle \in \mathsf{Lts} thread state

V \in \mathsf{View} \triangleq \mathsf{Loc} \to \mathsf{Time} \ \mathrm{view}

o_R \in \{rlx, acq\}

read access mode

\langle T, \dot{M} \rangle

thread configuration

o_W \in \{rlx, srlx, rel\} write access mode

m = \langle X @ f, v, t \rangle V \in \mathsf{Msg} message

\mathcal{T}:\mathsf{Tid}\to\mathsf{Lts}

thread state mapping

\pi \in \mathsf{Tid} \triangleq \{\pi_1, \pi_2, ...\} thread identifier

r = X \mathbf{0}(f, t] \in \mathsf{Rsv}

reservation

\langle \mathcal{T}, M \rangle

machine state

```

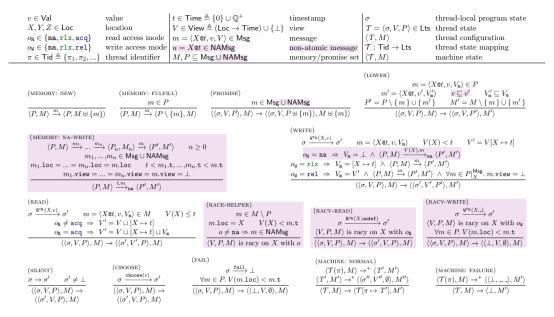

Figure 1.1: Domains and metavariables in PS2.1

```

(WRITE-HELPER)

(READ-HELPER)

(FULFILL-HELPER)

V(X) < t

m = \langle X \mathbf{Q}_{-}, .., t \rangle V_{\mathbf{m}} \in M

m = \langle X \mathbf{Q}_{-}, \underline{\ }, t \rangle V_{\mathbf{m}}

m = \langle X \mathbf{Q}_{-}, \underline{\ }, t \rangle \bot \in P

o_{\mathbf{R}} = \mathtt{rlx} \Rightarrow V' = V \sqcup [X \mapsto t]

o_{\mathtt{W}} \neq \mathtt{rel} \; \Rightarrow \; V_{\mathtt{m}} = \bot

o_{\mathtt{W}} = \mathtt{rlx}

o_{\mathtt{R}} = \mathtt{acq} \Rightarrow V' = V \sqcup [X \mapsto t] \sqcup V_{\mathtt{m}} \ o_{\mathtt{W}} = \mathtt{rel} \Rightarrow (V_{\mathtt{m}} = V \sqcup [X \mapsto t]) \land (P|_{X}^{\mathsf{Msg}} = \emptyset)

\langle V, M \rangle \xrightarrow{o_R, m}_R V'

\overline{\langle V, P, M \rangle \xrightarrow{o_{\mathtt{W}}, m}} \overline{\langle V \sqcup [X \mapsto t], P, M \uplus \{m\} \rangle}

\langle V, P, M \rangle \xrightarrow{o_{\mathbb{N}}, m}_{\mathbb{N}} \langle V \sqcup [X \mapsto t], P \setminus \{m\}, M \rangle

(READ)

\sigma \xrightarrow{R(o_R,X,v)} \sigma'

m = \langle X_{0}, v,  \rangle

m = \langle X_{0}, v, \rangle

m_{\rm R} = \langle X \mathbf{Q}_{\rm -}, v_{\rm R}, t \rangle_{\rm -} \qquad m_{\rm W} = \langle X \mathbf{Q} t, v_{\rm W}, {\rm \_} \rangle_{\rm -}

\langle V,M\rangle \xrightarrow{\ddot{o}_{\rm R},m_{\rm R}} V_{\rm R}

\langle V_{R}, P, M \rangle \xrightarrow{o_{W}, m_{W}} \langle V', P', M' \rangle

\langle V, P, M \rangle \xrightarrow{o_{W}, m}_{W} \langle V', P', M' \rangle

\langle \langle \sigma, \overline{V, P} \rangle, M \rangle \xrightarrow{\overline{W(o_{\overline{w}}, m)}} \langle \langle \sigma', V', P' \rangle, M' \rangle

\langle \langle \sigma, V, P \rangle, M \rangle \xrightarrow{\text{RMW}(o_R, o_W, m_R, m_W)} \langle \langle \sigma', V', P' \rangle, M' \rangle

(\langle \sigma, V, P \rangle, M) \xrightarrow{R(o_R, m)} (\langle \sigma', V', P \rangle, M)

(FAIL)

(PROMISE) / (RESERVE)

\sigma \xrightarrow{\mathtt{fail}} \bot

x \in \mathsf{Msg}

x \in \mathsf{Rsv}

r \in P \cap \mathsf{Rsv}

\langle \langle \sigma, V, P \rangle, M \rangle \xrightarrow{\text{fail}} \langle \langle \bot, V, \emptyset \rangle, M \rangle

\langle \langle \sigma, V, P \rangle, M \rangle \xrightarrow{\mathtt{prm} \ / \ \mathtt{rsv}} \langle \langle \sigma, V, P \uplus \{x\} \rangle, M \uplus \{x\} \rangle \qquad \overline{\langle \langle \sigma, V, P \rangle, M \rangle} \xrightarrow{\mathtt{cncl}} \langle \langle \sigma, V, P \setminus \{r\} \rangle, M \setminus \{r\} \rangle

```

Figure 1.2: Thread configuration steps in PS2.1

modify-writes (RMWs) carry two access modes—one for the read part and one for the write part. To simplify the presentation, we omit fences and release sequences. We also elide "system calls", used in [3, 4] to specify the observations of a given program. Instead, as we did when analyzing the examples above, we identify behaviors with final outcomes assigning values to certain registers. Nevertheless, our formal development [5] handles *all* features previously included in [3, 4] and uses system calls to define observable behaviors.

Figure 1.1 summarizes the different domains and (implicitly typed) metavariables. To define the **machine states**, besides a set Loc of locations and a set Val of values, we assume a set Time of timestamps which are rational numbers (totally and densely) ordered by < with 0 being the minimum value. A view,  $V \in Loc \rightarrow Time$ , records a timestamp for each location. We represent half-open ranges of timestamps using timestamp intervals denoted by (f,t] with f < t or f = t = 0. A machine state is a pair  $\langle \mathcal{T}, M \rangle$ , where:

• M, called memory, is a finite set of messages and reservations. A message m

takes the form  $\langle X @ f, v, t \rangle V$  where:  $X \in \mathsf{Loc}$ , (f, t] is a timestamp interval (t) is called the timestamp of m,  $v \in \mathsf{Val}$ , and  $V \in \mathsf{View}$  (called  $message\ view$ ). In turn, a reservation r = X @ (f, t] is defined like a message but without a value and a view. For a memory to be well-formed (as we implicitly assume henceforth), we require that messages/reservations with the same location have disjoint timestamp intervals; and that the view of each message is pointing to a timestamp of an existing message for every location. The initial memory consists of an initialization message  $\langle X @ 0, 0, 0 \rangle \bot$  for every location X, where  $\bot \triangleq \lambda X$ . 0 denotes the bottom view.

- $\mathcal{T}$  is a mapping assigning a thread state  $T = \langle \sigma, V, P \rangle$  to every thread  $\pi \in \mathsf{Tid}$ , where:

- $-\sigma$  records the (thread-local) program state. To keep the presentation abstract, rather than introducing a concrete syntax, we assume that the programming language is represented as a transition system, with local transitions labeled with the action that is performed. Each program state  $\sigma$  consists of the program code, the current program counter and local register file. To run PS2.1 on a program prog, we initialize the program state of each thread to include its part of prog and the initial program counter and register file.

- -V, called the *thread view*, records the highest timestamp that the thread has observed for each location.

- -P, called the *thread promise set*, is a set of messages and reservations recording the thread's outstanding promised and reserved writes. Since every promise and reservation is also added to the memory, we will always have  $P \subseteq M$ .

Importantly, we require thread states to be well-formed, where for every location X, the current view of  $\pi$  for X is lower than the timestamp of all of  $\pi$ 's outstanding promised writes for X (i.e.,  $\langle X \mathfrak{Q}_{-}, ., t \rangle_{-} \in P \Rightarrow V(X) < t$ ). This condition, called

promise-consistency in [4], is equivalent to saying that a thread should always be able to fulfill its promises by executing *some* sequence of operations (but not necessarily the sequence dictated by the program).

#### Figure 1.2 provides the **thread configuration steps**:

read. A thread with view V reads by picking a message  $\langle X @ f, v, t \rangle V_{m} \in M$  provided that  $V(X) \leq t$ , and updating its view for X to t. An acquire read operation incorporates the message view  $V_{m}$  in the thread view (the operator  $\sqcup$  "joins" views by taking the pointwise maximum).

write. A thread with view V writes by adding a message m to the memory whose timestamp is greater than the thread's view of X (V(X) < t). Non-release writes set the message view to the bottom view, whereas release writes record the thread view in the message view. Instead of adding a message, relaxed writes may fulfill outstanding promises by removing messages from the thread's set of promises. In addition, a release write to a location X forbids the existence of outstanding promises for X (denoted as  $P|_X^{\mathsf{Msg}} = \emptyset$ ).

**rmw**. A thread performs an RMW by first reading a message  $m_{\mathbb{R}} = \langle X \mathfrak{Q} f, v_{\mathbb{R}}, t \rangle V_{\mathbb{R}}$ , and then attaching a new message to the read message, *i.e.*, adding a message of the form  $m_{\mathbb{W}} = \langle X \mathfrak{Q} t, v_{\mathbb{W}}, t' \rangle V_{\mathbb{W}}$ . This results in consecutive messages (f, t], (t, t'], forbidding later writes from being placed between the two messages, which guarantees RMW atomicity.

promise. The main novelty of the promising model lies in its way to enable the reordering of a relaxed read followed by a relaxed write (to a different location). It does so by allowing threads to non-deterministically *promise* future (relaxed) writes, by simply adding messages to memory. Outstanding promises are recorded in the thread state, and removed when promises are fulfilled. As described below, to prevent "out-of-thin-air" behaviors (and validate DRF) the outstanding promises at every step are confined by the machine that requires *certification*—a thread that takes a step

should always be able to fulfill all its promises when executed in isolation.

reserve. To support register promotion and a more efficient mapping of RMWs to Arm (see Example 2 below), PS2.1 (as well as PS2, but unlike PS) allows threads to reserve timestamp intervals for their own future writes. Unlike promises, reservations do not commit on the *value* that will be used to fill the reserved interval, and thus cannot be read by other threads. They are only used to "block" timestamp intervals in the memory. As in the promise step, a thread adds the reservation to both the memory and its promise set.

**cancel**. A thread may cancel any of its reservations by simply removing it from the memory and its promise set.

fail. A thread can fail (modeling, e.g., division by 0 or an assertion failure) and invoke UB. Since UB can be replaced by any sequence of actions, this step is considered as fulfilling all of the thread's outstanding promises (here we need the well-formedness assumption on thread states).

The machine steps interleave thread configuration transitions as follows:

$$\frac{\langle \mathcal{T}(\pi), M \rangle \xrightarrow{\mathtt{cncl}}^* \xrightarrow{l} \xrightarrow{\mathtt{rsv}}^* \langle T', M' \rangle}{\langle T', M' \rangle \text{ is consistent}}$$

$$\frac{\langle T', M' \rangle \xrightarrow{\pi, l} \langle \mathcal{T}[\pi \mapsto T'], M' \rangle}{\langle \mathcal{T}, M \rangle \xrightarrow{\pi, l} \langle \mathcal{T}[\pi \mapsto T'], M' \rangle}$$

At each machine step, one thread is performing one thread step, possibly preceded by a sequence of reservation cancellations and followed by a sequence of reservations. Crucially, to ensure that promises do not make the semantics overly weak, a thread cannot take a step unless it reaches a *consistent* configuration, which is defined by:

**Definition 1** (Consistency). A thread configuration  $\langle T, M \rangle$  is *consistent* if  $\langle T, \widehat{M} \rangle \to^* \langle \langle -, -, \emptyset \rangle, - \rangle$  where  $\widehat{M}$ , called *capped memory*, is the memory obtained from M as follows:

(i) For every message/reservation on  $X\mathfrak{Q}(\_,t_1]$  and message/ reservation on  $X\mathfrak{Q}(f_2,\_]$  with  $t_1 < f_2$ , if there is no message/reservation in M with location X and timestamp  $t_1 < t < f_2$ , add a reservation  $X\mathfrak{Q}(t_1,f_2]$ ; and

(ii) For every message/reservation on  $X\mathfrak{Q}(\_, t_{\text{max}}]$  such that there is no message/reservation on  $X\mathfrak{Q}(\_, t]$  with  $t > t_{\text{max}}$ , add a reservation  $X\mathfrak{Q}(t_{\text{max}}, t_{\text{max}} + 1]$ .

Roughly speaking, consistency requires *certification*: the thread that took the step should be able to fulfill all its promises when executed in isolation. The certification starts from a *capped* version  $\widehat{M}$  of the current memory M, where all timestamp intervals between existing messages and reservations are blocked by reservations and a "cap reservation" is attached to the message with the highest timestamp for each location. As demonstrated in Example 3 below, a consequence of this is that promises cannot be made across RMW operations. (This is where the PS2.1 and PS2 differ; see [4].)

Behavior A behavior in PS2.1 are defined as follows.<sup>2</sup>

**Definition 2.** A behavior (in PS2.1) is a mapping  $r : \text{Tid} \to \text{Val}$  assigning a return value to each thread or  $r = \bot$  for erroneous termination. We inductively define when a state  $\langle \mathcal{T}, M \rangle$  generates a behavior r, denoted by  $\langle \mathcal{T}, M \rangle \Downarrow r$ :

$$\frac{\forall \pi \in \mathsf{Tid.}}{\mathcal{T}(\pi) = \langle \mathbf{return}(v_{\pi}), \_, \_ \rangle} \qquad \frac{\langle \mathcal{T}(\pi), M \rangle \to^* \langle \langle \bot, V, \emptyset \rangle, M' \rangle}{\langle \mathcal{T}, M \rangle \Downarrow r} \qquad \frac{\langle \mathcal{T}, M \rangle \to \langle \mathcal{T}', M' \rangle}{\langle \mathcal{T}, M \rangle \Downarrow r}$$

Below, we denote by  $[prog]_{PS2.1}$  the set of all behaviors of a program prog that are allowed in the PS2.1 semantics.

Remark 1. In [4] the machine step consists of any sequence of thread steps. We observe (and proved in Coq) that by using reservations and cancellations, it is possible to obtain a "normal form" for machine steps: a (possibly empty) sequence of cancellations, followed by a *single* thread step, followed by a (possibly empty) sequence of reservations. This normal form simplifies modular reasoning, as we can assume a consistent state when control is passed between the library code and the client code.

<sup>&</sup>lt;sup>2</sup>In Coq, a behavior is a sequence of system calls invoked during the program execution. The version in the chapter can be seen as the simplified case where the code of each thread ends with a  $\mathbf{return}(e)$  system call.

Next, we present several instructive examples involving RMWs. We refer the reader to [3, 4] for more examples related to the basic views and promises mechanisms.

**Example 1.** Two competing RMWs can never read from the same message in memory, as the following annotated program demonstrates:

$$a := \mathbf{FADD}(X, 1) / 0 \parallel b := \mathbf{FADD}(X, 1) / 0$$

(Upd)

Like **CAS**, we assume that **FADD** returns the value read before the update. Without loss of generality, suppose that  $\pi_1$  executes first. As it performs an RMW operation, it must "attach" the message it adds to an existing message. Since the only existing message in this stage is the initial one  $\langle X @ 0, 0, 0 \rangle \bot$ ,  $\pi_1$  will add  $m = \langle X @ 0, 1, t \rangle \bot$  with some t > 0 to the memory. Then, the RMW of  $\pi_2$  cannot also read from the initial message because this would require  $\pi_2$ 's message to be attached to the initial message, which would overlap with the (0, t] interval of m.

**Example 2.** The following annotated program illustrates a drawback of the original PS that prevents register promotion and the intended mapping to Armv8 [6]:

The annotated behavior is allowed by Armv8 (for the compiled program), and can be also obtained if the thread-local location Z is made a register. It is, however, disallowed by PS. PS2 and PS2.1 solve this problem using reservations. To observe  $a=1, \pi_1$  should be able to promise the write of 1 to Y at the beginning of the execution. This is not possible without reservations because  $\pi_1$  cannot update Z during the certification against the capped memory. However,  $\pi_1$  can reserve the interval (0,1] for the **FADD** before making the promise Y=1. Then, it can certify the promise Y=1 by using the reserved interval to perform the **FADD**. Intuitively speaking, while PS2.1 forbids the reordering of an RMW followed by a store, using reservations, it enables the reordering of the read part of the RMW before the read of X and the write part of the RMW after the write of Y, which more faithfully captures Arm's load-linked/store-conditional implementation.

**Example 3.** The following annotated program shows a behavior forbidden by PS2.1 because of its stronger certification requirement w.r.t. PS and PS2.

$$\begin{array}{ll} a := \mathbf{FADD}(X,1) & \text{//1} \\ Y^{\mathtt{rlx}} := 1 & c := \mathbf{FADD}(X,b) \end{array} \tag{RMW-W}$$

For  $\pi_1$  to read 1 via its **FADD**, it has to promise Y = 1. Unlike PS and PS2, this is not allowed in PS2.1 because  $\pi_1$  cannot perform **FADD** to X during the certification against the capped memory. Promising the **FADD** or reserving a space for it by  $\pi_1$  is impossible as well. Once  $\pi_1$  promises its **FADD**, it is committed to update X from 0 to 1. If  $\pi_1$  reserves a timestamp interval (0, t] for its **FADD**,  $\pi_2$  cannot update X from 0 to 1 since the X = 0 message is blocked by  $\pi_1$ 's reservation, again forcing  $\pi_1$  to update X from 0 to 1.

#### 1.2.2 Additional Examples of the Promising Semantics

We present several instructive examples to assist the reader in understanding the promising model.

**Example 4.** Consider the simple store-buffering litmus test:

$$X^{\text{rlx}} := 42$$

$$a := Y^{\text{rlx}} // \theta \qquad y^{\text{rlx}} := 37$$

$$b := X^{\text{rlx}} // \theta$$

(SB)

In this example, both threads are allowed to read 0 from the initialization messages. When  $\pi_1$  performs the write to X, it will add a message  $\langle X \mathfrak{C} f, 42, t \rangle \perp$  by choosing some  $t > f \geq 0$ . During this write,  $\pi_1$  should increase its view of X to t, while maintaining V(Y) to be 0 as it was. Hence,  $\pi_1$  is still allowed to read 0 from Y in the subsequent execution. As  $\pi_2$  can be executed in the same way, both threads are allowed to read 0.

**Example 5.** To see how release/acquire synchronization works consider the simple message passing litmus test:

$$X^{\text{rlx}} := 1$$

$$Y^{\text{rel}} := 1$$

$$a := Y^{\text{acq}} //1$$

if  $a = 1$  then

$$b := X^{\text{rlx}} // \neq 0$$

(MP)

Here, if  $\pi_2$  reads 1 from Y, which is written by  $\pi_1$ , both threads are synchronized through release and acquire. Thus,  $\pi_2$  obtains the knowledge of  $\pi_1$ , namely its view for X is increased to include the timestamp of  $X^{\text{rlx}} := 1$  of  $\pi_1$ . Therefore, after reading 1 from Y,  $\pi_2$  is not allowed to read the initial value from X.

**Example 6.** To see how promises work consider the simple load buffering litmus test:

$$a := X^{\text{rlx}} //1 \mid b := Y^{\text{rlx}} //1 Y^{\text{rlx}} := 1 \quad X^{\text{rlx}} := b$$

(LB)

To obtain the annotated behavior (which has to be allowed in a model supporting load-store reordering of relaxed accesses),  $\pi_1$  may promise  $Y^{\text{rlx}} := 1$  at first. This allows  $\pi_2$  to read 1 from Y and write it back to X. Then,  $\pi_1$  can read 1 from X, which was written by  $\pi_2$ , and fulfill its promise. Note that at the point of promising  $Y^{\text{rlx}} := 1$  (in the very beginning of the run),  $\pi_1$  can run and perform  $Y^{\text{rlx}} := 1$  without any "help" of other threads, so it reaches a consistent thread state after making the promise.

**Example 7.** Certification, the thread-local run fulfilling all outstanding promises of the thread, is necessary to avoid "thin-air reads" as demonstrated by the following variant of LB:

As every thread simply copies the value it reads, both threads are not supposed to read any non-0 value. In the promising semantics, if a thread could promise without certification, this behavior would be allowed by the same execution as the one for LB above. However, with the certification requirement,  $\pi_1$  cannot promise  $Y^{\text{rlx}} := 1$ , as, when running in isolation,  $\pi_1$  only writes  $Y^{\text{rlx}} := 0$ .

## Chapter 2

## Local Data-Race-Freedom Guarantees for Program Writers

## 2.1 Introduction: The Need for Local DRF

Designing a programming language shared-memory concurrency semantics, a.k.a. a weak memory model, is a complex task. On the one hand, one aims to allow mappings to commodity modern architectures (such as x86, Power, Arm, and RISC-V) that will not subvert the hardware's extensive optimization efforts, as well as to validate certain compiler optimizations that are unsound under a strong semantics such as sequential consistency (SC). On the other hand, since the introduction of weak memory semantics in programming languages, it was clear that the majority of programmers will need to program and reason about their code without understanding the full complexities of the underlying semantics. Hence, to be useful and amenable to reasoning, a memory model has to (i) ensure strong and intuitive semantics for programs that follow certain programming disciplines; and (ii) allow programmers to adhere to such disciplines even without knowing the actual underlying weak semantics.

A fundamental programmability guarantee of this kind is DRF-SC [7]. It ensures that data-race free programs (avoiding races using locks or designated synchronization accesses) only exhibit SC behaviors. Crucially, data-race freedom (DRF), the premise of DRF-SC, is only required to hold *under SC*, allowing programmers to use this guarantee knowing nothing about the underlying complex model, but rather naively imagining standard interleaving semantics that follows the program order and employs a conventional memory.

Since SC is sometimes considered overly expensive to ensure efficient implementations (and as building blocks for establishing DRF-SC), more refined DRF guarantees have been studied in the last few years [3, 8]. Each of these guarantees is applicable on a different level of accesses—requiring more restrictive race-freedom conditions and resulting in stronger semantics guarantees. In particular, in models with release/acquire (RA) accesses, one aims to ensure RA semantics for programs that exhibit no races on accesses weaker than RA accesses. This guarantee, called DRF-RA [3], allows programmers to use (non-racy) weaker (and more efficient) accesses than RA accesses while knowing only the RA semantics. The latter, although weaker than SC, is much simpler than the full underlying model, and it admits several verification methods and tools, including model checkers and program logics [9, 10, 11, 12]. Similarly, on the level of "relaxed" accesses, which are weaker than RA ones and intended to be compiled to plain machine loads and stores, a DRF guarantee with respect to an "in-order" RC11-like [13] semantics (with no load buffering behaviors) ensures in-order semantics when, under the in-order semantics, races on relaxed accesses are properly confined (see DRF-PF in [3] and DRF-RLX in [8]). Again, the benefit is significant: an in-order semantics like RC11 is significantly simpler than an "out-of-order" model in which reads can read from later writes, and like SC and RA, "in-order" models admit several verification methods [14, 15, 16, 17].

Nevertheless, the global nature of all DRF guarantees mentioned above makes

them only applicable when the whole program admits the required race freedom premise. Software, however, is modularly developed, often without access to the full code. Moreover, benign races in carefully crafted concurrency libraries make the DRF guarantees futile for reasoning by clients that use these libraries, leaving them with no formal assurances applicable without a complete understanding of the underlying model (see Fig. 2.1 for an illustrative example).

This drawback of the DRF guarantees is addressed by more refined "local" guarantees that can be applied also on parts of a given program [18, 19]. In particular, a local DRF (LDRF, for short) guarantee allows one to conclude that accesses to certain shared locations have stronger semantics provided that when assuming stronger semantics to these locations, the program exhibits no races on them. The important practical consequence is that it is safe to assume that the client portion of the code is running under the stronger semantics when races are completely confined in the library code. Moreover, clients may rely on the synchronization guarantees provided by libraries to establish race freedom of their code while still understanding only the stronger semantics.

Unfortunately, the negative observation of this chapter is that LDRF guarantees of this kind are inconsistent with compiler optimizations that are normally expected to be sound in weak memory models. To demonstrate this, we present examples that, under very minimal assumptions on the underlying model, are locally race free, but a sequence of program transformations that are intended to be sound entails that they must have a behavior that violates LDRF. Viewing these guarantees as essential for modular software development, we believe that this reveals a severe limitation on the usefulness of models that support the full range of optimizations.

On the positive side, we observe that by disabling a certain problematic compiler optimization, an LDRF guarantee w.r.t. an "in-order" RC11-like semantics becomes

achievable. Concretely, we identify that RMW-store reordering<sup>1</sup> is the source of the problem and show that by disabling only these reorderings one is able to validate a critical LDRF guarantee. In turn, for (naive formulations of) LDRF-RA/SC, disabling RMW-store reordering does not suffice, and we address the problem by slightly strengthening the (naive) race-freedom premise. The resulting guarantees are useful for modular reasoning (as demonstrated in §2.4), and we are not aware of any non-contrived example where this strengthened race-freedom condition makes a difference.

To establish that forbidding RMW-store reordering and slightly strengthening the race-freedom premise suffice for establishing the LDRF guarantees, we demonstrate a particular model that satisfies the desiderata. Concretely, we prove that three LDRF guarantees are validated by PS2.1, a variant of the promising semantics, mentioned as a possible simplification of PS2 in [4, §4.4], that supports all standard (local and global) optimizations excluding RMW-store reordering.

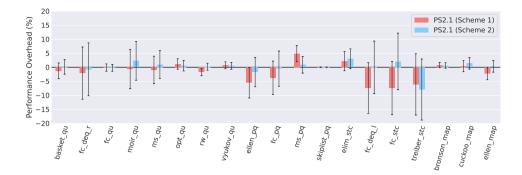

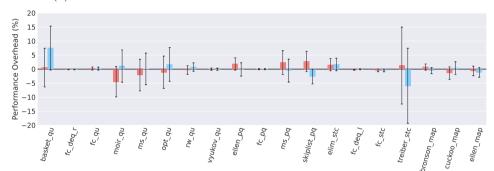

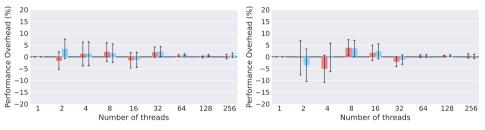

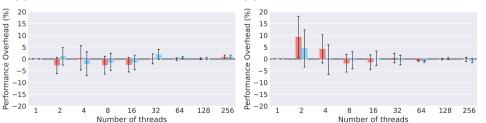

In addition to the theoretical results, we empirically investigate the cost of forbidding RMW-store reorderings, and observe that it is negligible in practice. Current standard compilers are very conservative with reorderings of atomic accesses [21], and mainstream architectures, except Armv8, do not allow RMW-store reordering. Even in Armv8, it is relevant only for non-acquire unconditional RMWs (i.e., FADD or XCHG, but not CAS), for which a "fake" branch instruction is needed to prevent the reordering. Since FADDs and XCHGs are not executed frequently and fake branching is relatively cheap [21], we expect the implementation cost to be negligible in practice. We have performed a sequence of experiments that validate this hypothesis (§2.5).

As for the LDRF guarantees, we formulate three guarantees, and prove them

<sup>&</sup>lt;sup>1</sup>RMW (read-modify-write) operations, such as compare-and-swap (**CAS**), fetch-and-add (**FADD**) and atomic exchange (**XCHG**), atomically perform a read followed by a write to the same location. Certain models—e.g., C11 [20], the promising semantics [3], and Weakestmo [8]—allow the reordering of non-acquire RMWs with subsequent relaxed writes to a different location.

```

egin{aligned} r_0 &:= \mathbf{pop\_wait}(S) \ \mathbf{lock}() \ \mathbf{process} \ r_0 \ \mathbf{accessing} \ \pmb{X}, \ \pmb{Y} \ \mathbf{unlock}() \end{aligned} \qquad egin{aligned} r_1 &:= \mathbf{pop\_wait}(S) \ \mathbf{lock}() \ \mathbf{process} \ r_1 \ \mathbf{accessing} \ \pmb{X}, \ \pmb{Y} \ \mathbf{unlock}() \end{aligned}

```

Two threads are popping "work items" from a wait-free (possibly, relaxed) stack S, and use a lock to perform the work for avoiding races on shared locations X and Y. The DRF-SC guarantee does not allow the client to show that the accesses to X and Y inside the locked regions do not have weak behaviors. Indeed, the program is not race free due to benign races in the implementation of the pop operation (in fact, if lock/unlock are not primitives, then the implementation of the lock itself is racy as well). In contrast, a local DRF-SC guarantee allows clients to use the specification of the lock to conclude that the accesses to X and Y are not racy, and therefore, they can safely assume SC semantics for X and Y.

Figure 2.1: A simple example demonstrating the weakness of the global DRF-SC guarantee

for PS2.1, where each of which provides the key lemma for establishing the next one: (1) LDRF-PF w.r.t. the *promise-free* (RC11-like) semantics allowing one to restrict "promises"—a special mechanism that accounts for load-store reorderings in the promising semantics, which is undoubtedly the most complicated and hard to reason about component of the model; (2) LDRF-RA w.r.t. release/acquire semantics; and (3) LDRF-SC w.r.t. SC semantics.<sup>2</sup>

To conclude, our contributions are summarized as follows:

- 1. We show that the full set of compiler optimizations is inconsistent with local DRF guarantees (§2.2).

- 2. We establish the consistency of three local DRF guarantees (LDRF-PF, LDRF-RA,

<sup>&</sup>lt;sup>2</sup>Although allowing races on SC accesses is essentially needed for *global* DRF-SC (otherwise there are no means of synchronization), it is unnecessary for *local* DRF-SC because synchronization is typically provided by library methods. Thus, LDRF-SC is still applicable for the promising semantics, which currently lacks specialized SC accesses.

- and LDRF-SC) and all standard optimizations excluding RMW-store reordering by proving that PS2.1 validates them all (§2.3).

- 3. We outline the applicability of local DRF for reasoning about client code, as well as library code (§2.4).

- 4. We empirically observe that the performance impact of disabling RMW-store reorderings is negligible (§2.5).

Our LDRF proofs in §2.3 are fully mechanized in Coq. The formalization is available at [5].

## 2.2 Local DRF in Weak Memory Models

In this section we demonstrate the inherent tension between local DRF guarantees and standard compiler optimizations. While our results in the next sections are specific to the promising semantics, the discussion in this section is general, making its implications applicable in other models as well.

## 2.2.1 Local DRF w.r.t. an "In-Order" Semantics

By far, the most complicated aspect of a weak memory semantics is related to allowing load-store reordering of possibly racy independent relaxed accesses (a.k.a. load buffering behaviors). This is the source of the infamous "out-of-thin-air" problem [22], the reason why per-execution declarative models cannot work and more complicated event-structure-based models are needed instead [23, 8], and the only rationale behind "promises" in the promising semantics. To circumvent this complexity, one can use less efficient stronger models, such as RC11 [13], that conservatively forbid load-store reorderings altogether (by disallowing cycles in the union of the program order and the reads-from relation), and thus cannot map relaxed accesses to plain machine loads and stores in architectures like Arm.

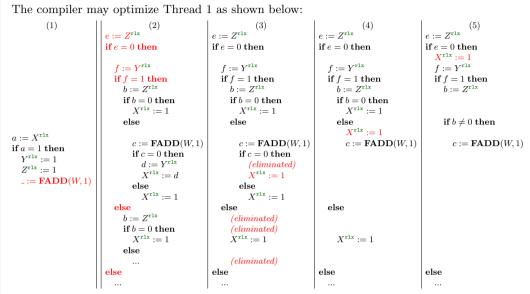

The compiler may optimize Thread 1 as shown below:

- (1) reorder the read c := L to be second, after introducing the same read c := L in the else-branches (when  $b \neq 0$  or a = 0);

- (2) insert a dummy if-then-else on c = 1 and distribute the rest of the code to both branches ("trace-preserving" transformation);

- (3) forward the write Y := 0 to the read  $a := Y^{rlx}$  in the else-branch, turning it into a := 0;

- (4) distribute the branch on  $a \neq 0$  to both prior branches on c = 1 and optimize them: eliminate repeated redundant testing of c = 1 in the then-branch, and remove dead code in the else-branch ("trace-preserving" transformation);

- (5) merge  $b := \mathbf{CAS}(X, 0, 42)$  and if b = 0 then  $X^{\mathtt{srlx}} := 37$  into  $b := \mathbf{CAS}^{\mathtt{srlx}}(X, 0, 37)$ .

Now, the compiler may optimize Thread 2 as shown below:

- (1) noticing that  $X \neq 42$  is a global invariant (42 is never written to X), optimize away the redundant test "if  $(d \neq 42)$  then";

- (2) reorder the independent **CAS** on X and write to L.

Figure 2.2: Program transformations on LDRF-PF-Fail (in the final transformed program, we may get d = 37 even under SC!)

We generally refer to RC11-like models as "in-order" models, as they are captured by transition systems that execute memory accesses according to their program order while ensuring that every read reads from a previously executed write. More formally, this property is defined as follows:

**Definition 3.** A memory model M is *in-order* if every behavior allowed by M corresponds to a trace of memory accesses that respects the program order such that every read r of value v from location X is justified by some write w that writes v to X and appears in the trace before r.

This definition covers a wide variety of (not so weak) memory models including RC11, TSO [24], causal consistency [25, 26], the OCaml model in [18], and (of course) SC. It ensures a conceptually simple semantics and enables several verification approaches [14, 15, 16, 17].

A natural approach to allow "in-order" reasoning for a given program in a model with (fully) relaxed accesses is to use a DRF guarantee. When such guarantee is provided, one is able to assume in-order semantics for programs that under in-order semantics exhibit no races on accesses annotated as relaxed (so that the guarantee can be applied knowing nothing about the out-of-order part of the semantics). Moreover, as demonstrated in §2.1, for being applicable in a modular fashion (e.g., in the presence of unrelated races induced by some library methods over which the client has no control), this guarantee has to be local.

To give a more precise statement of such a local DRF guarantee (but still keep the discussion general), consider an arbitrary model M with relaxed reads/writes, intended to be compiled to plain machine accesses, and "strong relaxed" writes, intended to be compiled with barriers to forbid the hardware from reordering a load followed by a strong relaxed write.<sup>3</sup> Strong relaxed writes provide "in-order" semantics in the

<sup>&</sup>lt;sup>3</sup>Strong relaxed accesses were introduced in [3] as a technical tool for establishing the correctness of mapping to hardware. They are also useful in the current discussion. Like release writes, they forbid reordering with preceding reads; but unlike release writes, they are not intended to synchronize with reads by other threads.

following sense: Every behavior allowed by M corresponds to some trace of memory accesses that respects the program order such that: (i) every read r of value v from location X is justified by some write w that writes v to X and appears in the trace; and (ii) if r is justified by w that is strong relaxed, then w should appear before r in the trace. (Note that M allows a read r to be justified by a relaxed write that is executed after r.)

Then, a local DRF guarantee w.r.t. an in-order semantics for M is stated as follows: For every set  $\mathcal{L}$  of locations, every behavior of a given program prog allowed by M is allowed by M for prog when all writes to locations in  $\mathcal{L}$  are considered strong relaxed, provided that under this assumption prog exhibits no races involving writes to locations in  $\mathcal{L}$  that are annotated as relaxed.

For example, this guarantee (for  $\mathcal{L} = \{L\}$ ) allows one to show that the annotated behavior in the following program is disallowed in the model M without knowing anything besides an in-order semantics:<sup>4</sup>

$$\begin{array}{ll} a := {\color{red} L^{\tt rlx}} & \parallel \ b := X^{\tt rlx} \ \ \, \mbox{$/[t]$} \\ {\color{blue} {\bf libfun_1}()} & | \ \ \, \mbox{$\bf libfun_2()$} \\ X^{\tt srlx} := a & | \ \ \, \mbox{$\bf if} \ b = 1 \ \mbox{{\bf then}} \ \, {\color{blue} L^{\tt rlx}} := 1 \ \mbox{else} \ \, {\color{blue} L^{\tt srlx}} := 1 \end{array} \tag{LDRF-LB} \end{array}$$

where  $\mathbf{libfun_1}()$  and  $\mathbf{libfun_2}()$  are calls to some library methods that execute racy relaxed code accessing a set of locations disjoint from X and L. Indeed, assuming that  $L^{r1x} := 1$  has strong relaxed semantics, all writes to X and L are strong relaxed, and the in-order property easily entails that  $L^{r1x} := 1$  (in the then-branch) is never executed and thus not involved in a race. Then, the premise of the LDRF guarantee above holds, and one concludes, again based on the in-order property, that b = 1 is disallowed by M. Crucially, this reasoning does not require any knowledge of how exactly M behaves for (fully) relaxed writes (which, in fact, we have not specified). We also note that a global DRF guarantee cannot be used due to the presence of racy

<sup>&</sup>lt;sup>4</sup>We assume that all locations are initially 0, and that the "default" access mode is relaxed (so we omit rlx annotations).

code in the library methods.

Unfortunately, we observe that this LDRF guarantee is actually inconsistent with program optimizations that are standardly intended to be sound in weak memory models. Indeed, the following example shows that any such model M cannot validate both the LDRF guarantee and all standard optimizations:<sup>5</sup>

$$\begin{array}{l} Y := 0 \\ a := Y^{\text{rlx}} \\ \textbf{if } a \neq 0 \textbf{ then} \\ b := \mathbf{CAS}(X, 0, 42) \\ \textbf{if } b = 0 \textbf{ then} \\ c := L^{\text{rlx}} \\ \textbf{if } c = 1 \textbf{ then} \\ X^{\text{srlx}} := 37 \end{array} \qquad \begin{array}{l} Y := 1 \\ d := \mathbf{CAS}(X, 0, 1) \text{ $/\!\!/37$ ?} \\ \textbf{if } d \neq 42 \textbf{ then} \\ L^{\text{rlx}} := 1 \end{array} \tag{LDRF-PF-Fail}$$

where  $CAS(X, v_1, v_2)$  reads a value from X; if it is equal to  $v_1$  (i.e., successful), writes  $v_2$  to X ensuring atomicity between the read and write, and otherwise (i.e., unsuccessful) does nothing; and finally returns the read value.

Indeed, assuming that the write to L has strong relaxed semantics, it is easy to see that no execution of the program executes both  $c := L^{r1x}$  and  $L^{r1x} := 1$ , and hence there is no race on L. Specifically, if such execution is allowed by the model M, then the **CAS** of the second thread must read 37 due to the standard RMW atomicity (which implies that two successful CAS instructions cannot read from the same write), and so  $c := L^{r1x}$  must read 1. However, since 37 is written by a strong relaxed write, it follows that  $X^{sr1x} := 37$  appears in the trace before  $d := \mathbf{CAS}(X, 0, 1)$ . This implies that  $c := L^{r1x}$  appears in the trace before  $L^{r1x} := 1$ , which contradicts the assumption that  $L^{r1x} := 1$  has strong relaxed semantics.

Now we can demonstrate the inconsistency between the local DRF guarantee above and program optimizations. Since the premise of the guarantee is satisfied (for  $\mathcal{L} = \{L\}$ ), if the guarantee holds, we may assume that  $L^{r1x} := 1$  has strong relaxed

<sup>&</sup>lt;sup>5</sup>We are not aware of a smaller example that can be used for this purpose.

semantics, and conclude, by the exact same reasoning, that the d=37 outcome is disallowed (no execution executes both  $c:=L^{r1x}$  and  $L^{r1x}:=1$ ). Nevertheless, Fig. 2.2 shows that starting from this program, a sequence of transformations, each of which is intended to be sound in standard weak memory models, may actually lead to the d=37 outcome!

As a concrete example for a model M, consider the PS2 model [4], which satisfies the above assumptions and validates all transformations used in Fig. 2.2. (In PS2, strong relaxed writes correspond to relaxed writes that cannot be promised ahead of their execution.) It follows that PS2 fails to admit the above guarantee w.r.t. an in-order semantics.<sup>6</sup>

To locate the source of the problem, we observe that RMW-store reordering (applied in the second thread's code in Fig. 2.2) is the transformation that breaks a key property, which we call promise monotonicity (formally stated in §2.3.1), needed for our proof. Indeed, one of the main ideas in proving local DRF is to show that relaxed store hoisting (moving a relaxed write to be before other instructions) does not allow more behaviors unless the store was racy before the code motion. However, this property fails if reordering of a relaxed RMW followed by a relaxed write to a different location is allowed. For instance, in the program above, executing  $d := \mathbf{CAS}(X, 0, 1)$  before  $L^{r1x} := 1$  prevents the behavior executing both  $L^{r1x} := 1$  and  $c := L^{r1x}$ , but executing them in the opposite order allows that behavior.

Accordingly, to accomplish our proof, we switched to PS2.1, a variant of the PS2 model outlined in [4, §4.4], which gives up RMW-store reordering for simplicity and better meta-theoretic properties such as the absence of deadlocking executions.<sup>7</sup> For PS2.1 we are able to prove LDRF-PF—a local DRF guarantee with respect

<sup>&</sup>lt;sup>6</sup>The original promising model PS [3] does not admit global value-range analysis, which is needed in the sequence of transformations in Fig. 2.2. Nevertheless, in §2.6, we present a similar (yet more intricate) counterexample for PS.

<sup>&</sup>lt;sup>7</sup>We have formally established the absence of deadlocks in Coq [5].

to the promise-free fragment of the promising semantics (an in-order model), thus establishing the consistency of such a local DRF guarantee with all optimizations except for RMW-store reordering.

#### 2.2.2 Local DRF w.r.t. RA and SC

For less advanced users, an in-order RC11-like semantics may still be hard to reason with. Then, one needs local DRF properties w.r.t. stronger fragments like release/acquire semantics (LDRF-RA) or even sequential consistency (LDRF-SC). Next, we discuss the subtlety in stating and achieving these local guarantees in a general model that supports load-store reordering of relaxed accesses. We focus on LDRF-RA, but the discussion is the same for LDRF-SC.

A naive notion of LDRF-RA can be naturally derived from the global DRF-RA guarantee. The latter ensures that a program has only RA behaviors provided that under RA semantics it exhibits no races involving accesses annotated as (strong) relaxed [3]. To "localize" this guarantee with respect to a given set  $\mathcal{L}$  of locations, we need to consider " $\mathcal{L}$ -RA behaviors"—behaviors in which accesses to locations in  $\mathcal{L}$  are treated as RA accesses (even when annotated with weaker modes), but other accesses are interpreted as annotated in the program. Then, a naive LDRF-RA guarantee would say that a program has only  $\mathcal{L}$ -RA behaviors provided that its  $\mathcal{L}$ -RA behaviors exhibit no races involving accesses to locations in  $\mathcal{L}$  annotated with access modes weaker than release and acquire.

We show that in any sensible weak memory model this guarantee is actually inconsistent with standard program optimizations (here, RMWs are not involved at all).

Specifically, the  $\{L\}$ -RA behaviors of the program on the right exhibits no races on the location L, but a sequence of standard optimizations may lead to a non  $\{L\}$ -RA

behavior, which invalidates the naive LDRF-RA guarantee.

$$\begin{array}{l} a := Y^{\text{rlx}} \quad \# 1 \; ? \\ \textbf{if} \; a = 1 \; \textbf{then} \\ b := L^{\text{rlx}} \\ X^{\text{rlx}} := b \\ \textbf{else} \\ X^{\text{rlx}} := 1 \end{array} \qquad \begin{array}{l} c := X^{\text{rlx}} \\ L^{\text{rlx}} := 1 \\ Y^{\text{rlx}} := c \end{array} \qquad \text{(Naive-LDRF-RA-Fail)}$$

To see this, we first claim that in any sensible model, assuming that the accesses to L are RA, the first thread cannot read 1 from Y. Indeed, if  $a := Y^{r1x}$  reads 1, it easily follows that  $b := L^{r1x}$  reads from  $L^{r1x} := 1$ . However, with the assumption that the accesses to L are interpreted as RA accesses, the latter implies a "happens-before" path from  $c := X^{r1x}$  to  $X^{r1x} := b$ , which implies that  $c := X^{r1x}$  cannot read from  $X^{r1x} := b$ . In turn, the value 1 is never written to Y.

Second, with the same assumption (that the accesses to L are RA), the above reasoning also shows that there are no races on L. In fact, the exact definition of a race does not matter here: we actually know that the first thread will not access L at all. Then, the naive LDRF-RA for  $\mathcal{L} = \{L\}$  implies that the program has only  $\{L\}$ -RA behaviors, which, as argued above, entails that the a=1 outcome is disallowed. Nevertheless, in Fig. 2.3, we show that starting from the above program, a sequence of program transformations, each of which is intended to be sound in standard weak memory models, may actually lead to this outcome!

What went wrong? In the analysis above, we used a racy access (to L) to establish synchronization, and then used this synchronization to invalidate the racy execution itself. However, when the racy read is performed as a relaxed read it does not induce synchronization, and nothing actually forbids the candidate racy execution. To solve this problem, we have to strengthen the premise of LDRF-RA, so that synchronization induced by racy reads (from locations in  $\mathcal{L}$ ) cannot be used to eliminate races.

A possible way to do so is to weaken the semantics of "racy reads" from locations

The compiler may optimize Thread 1 as shown below:

- (1) reorder the read b := L to be first, after introducing the same read b := L in the else-branch (when  $a \neq 1$ );

- (2) insert a dummy if-then-else on b = 1 and distribute the rest of the code to both branches ("trace-preserving" transformation);

- (3) in the then-branch on b = 1, substitute b with 1 and merge both branches on a = 1 ("trace-preserving" transformation);

- (4) reorder the independent read from Y and write to X.

In addition, the compiler may optimize Thread 2 as shown below:

$$\begin{array}{c|c} (0) & (1) \\ c := X^{{\tt rlx}} & L^{{\tt rlx}} := 1 \\ L^{{\tt rlx}} := 1 & c := X^{{\tt rlx}} \\ Y^{{\tt rlx}} := c & Y^{{\tt rlx}} := c \end{array}$$

(1) reorder  $c := X^{rlx}$  and  $L^{rlx} := 1$ .

Figure 2.3: Program transformations on Naive-LDRF-RA-Fail (after the transformations, we may get a = 1 even under SC!)

in  $\mathcal{L}$  in the  $\mathcal{L}$ -RA semantics, and say that unlike standard acquire reads, these reads do not induce synchronization. However, this solution would require a precise definition of the semantics of racy reads, which goes beyond standard RA semantics.

In this paper, we follow an alternative approach that involves a certain over-approximation—we will say that a racy read simply invokes undefined behavior (UB). Since UB includes any possible behavior, the race-freedom condition based on racy reads invoking UB implies the one where racy reads do not induce synchronization. In other words, we will say that a race occurs if some racy read is reachable ignoring what happens after the racy read is executed. With this definition, relying on the previously mentioned LDRF-PF as a key lemma, we proved LDRF-RA (and LDRF-SC) for PS2.1.8 Importantly, unlike C11's "catch-fire" semantics, UB for races is not a part of the concurrency semantics (indeed, the promising semantics provides means to avoid "catch-fire"), but is only used for defining races when establishing the premise of LDRF-RA/SC. We note that a similar strengthening of the race-freedom premise in LDRF-PF does not solve the problem outlined in §2.2.1 (LDRF-PF-Fail is still a counterexample).

## 2.3 Local DRF Guarantees

In this section we present our local DRF results for PS2.1.

We note that, unlike the conventional DRF theorems, write-write races are only considered as races for LDRF-SC. The other results, LDRF-PF and LDRF-RA only require the absence of certain read-write races.

We present the statements of "time-wise" local DRF guarantees in §2.3.4. Roughly speaking, these time-wise guarantees apply when no race occurs between two states in the machine trace and they ensure the stronger semantics between these two states.

<sup>&</sup>lt;sup>8</sup>PS2 does not satisfy our LDRF-RA/SC theorems (LDRF-PF-Fail is a counterexample for them as well).

All results of this section (including time-wise LDRF) are fully mechanized in Coq ( $\sim 35 K$  LoC altogether) [5].

#### 2.3.1 Local DRF-PF

The first step for formulating LDRF-PF is to formally define an "in-order" restriction of PS2.1 w.r.t. a given set  $\mathcal{L}$  of locations. This can be simply defined by forbidding promises to the locations in  $\mathcal{L}$ .

**Definition 4.** Given a set  $\mathcal{L} \subseteq \mathsf{Loc}$ , the  $\mathcal{L}\text{-}PF\text{-}machine}$  is the strengthening of PS2.1 obtained by forbidding the application of the (PROMISE) rule for locations in  $\mathcal{L}$ . We denote by  $[\![prog]\!]_{\mathrm{PF}}^{\mathcal{L}}$  the set of all behaviors of a program prog allowed by the  $\mathcal{L}\text{-}PF\text{-}machine}$ .

Next, we define what a racy execution in the  $\mathcal{L}$ -PF-machine is. Roughly, an execution is  $\mathcal{L}$ -racy if it includes some thread  $\pi_1$  taking a machine step writing a message m to a location in  $\mathcal{L}$  by a relaxed write, immediately followed by another thread  $\pi_2$  taking a sequence of machine steps that ends with reading the message m.

**Definition 5.** An execution in the  $\mathcal{L}$ -PF-machine is  $\mathcal{L}$ -racy if it includes a sequence of machine steps of the form:

$$\xrightarrow{\pi_1,l_1} \xrightarrow{\pi_2,-} * \xrightarrow{\pi_2,l_2} \xrightarrow{}$$

with  $\pi_1 \neq \pi_2$ ,  $l_1 \in \{W(\text{rlx}, m), RMW(\_, \text{rlx}, \_, m)\}$  and  $l_2 \in \{R(\_, m), RMW(\_, \_, m, \_)\}$  for  $m \in \mathsf{Msg}$  with location  $L \in \mathcal{L}$ .

Then, LDRF-PF is formulated as follows.

**Theorem 1** (LDRF-PF). If there is no  $\mathcal{L}$ -racy execution of prog in the  $\mathcal{L}$ -PF-machine, then  $[prog]_{PS2,1}^{\mathcal{L}} = [prog]_{PF}^{\mathcal{L}}$ .

**Remark 2.** While the  $\mathcal{L}$ -PF-machine forbids promises to locations in  $\mathcal{L}$ , it still allows making reservations to these locations. Nevertheless, the  $\mathcal{L}$ -PF-machine is an in-order semantics w.r.t.  $\mathcal{L}$  since threads cannot read from reservations. Moreover, the only purpose of making reservations to  $\mathcal{L}$  is to allow certain promises to locations not in  $\mathcal{L}$ . Hence, reservations to  $\mathcal{L}$  can be ignored in the typical use of LDRF that over-approximates the behaviors of locations not in  $\mathcal{L}$  to be completely unconstrained.

Revisiting LDRF-PF-Fail, the argument outlined in §2.2 shows that no execution of LDRF-PF-Fail in the  $\{L\}$ -PF-machine is L-racy. Then, from Thm. 1, it follows that the d=37 outcome is disallowed for that program under PS2.1.

**Example 8.** As an instructive example of an application of LDRF-PF, we show that no execution of the following program in the  $\{X,Y\}$ -PF-machine is  $\{X,Y\}$ -racy, and so  $[prog]_{PS2.1} = [prog]_{PF}^{\{X,Y\}}$ .

$$X^{\mathtt{rlx}} := 1 \quad || \quad a := Y^{\mathtt{rlx}} \\ Y^{\mathtt{rel}} := 1 \quad || \quad \mathbf{if} \ a = 1 \ \mathbf{then} \\ Z^{\mathtt{rlx}} := 1 \quad || \quad b := Z^{\mathtt{rlx}} \\ \mathbf{if} \ b = 1 \ \mathbf{then} \\ c := X^{\mathtt{rlx}}$$

(MP2)

Clearly, there is no race on Y since the program has no relaxed writes to Y (syntactically). Now, assuming no promises on X and Y, the write to Z in  $\pi_2$  can neither be promised nor executed before  $\pi_1$  executes the write to Y. Similarly, the read from X in  $\pi_3$  cannot be executed before  $\pi_2$  promises or executes the write to Z. Therefore, the write to Y in  $\pi_1$  should be first executed in order for  $\pi_3$  to execute the read from X, and thus there is no X-racy execution in the  $\{X,Y\}$ -PF-machine.

**Proof sketch of LDRF-PF** We highlight the main ideas in the proof of Thm. 1, which is the most challenging among our results. For its proof, we introduce an intermediate semantics, called  $\mathcal{L}$ -PRF-machine, and define the notion of race in this machine (PRF stands for promise-read-free).

**Definition 6.** Given a set  $\mathcal{L} \subseteq \mathsf{Loc}$ , the  $\mathcal{L}\text{-}PRF\text{-}machine}$  is the strengthening of PS2.1 obtained by forbidding steps reading from promises to locations in  $\mathcal{L}$ . We denote by  $\llbracket prog \rrbracket_{\mathsf{PRF}}^{\mathcal{L}}$  the set of all behaviors of a program prog allowed by the  $\mathcal{L}\text{-}PRF\text{-}machine}$ .  $\mathcal{L}\text{-}racy$  executions in the  $\mathcal{L}\text{-}PRF\text{-}machine}$  are defined exactly as in Def. 5.

Then, we prove the following three lemmas for every program prog, from which Thm. 1 directly follows:

- (i)  $[prog]_{PRF}^{\mathcal{L}} \subseteq [prog]_{PF}^{\mathcal{L}}$ .

- (ii) If there is no  $\mathcal{L}$ -racy execution of prog in the  $\mathcal{L}$ -PRF-machine, then  $[\![prog]\!]_{PS2.1}^{\mathcal{L}} \subseteq [\![prog]\!]_{PRF}^{\mathcal{L}}$ .

(iii) If there is an  $\mathcal{L}$ -racy execution of prog in the  $\mathcal{L}$ -PRF-machine, then there is one in the  $\mathcal{L}$ -PF-machine.

Next, we only discuss (ii), and identify an essential property of PS2.1, which we call *promise monotonicity*, that is needed in our proof.

To prove (ii), we use the following "reshuffling" mechanism: when thread  $\pi_1$  can take a sequence seq of thread steps reading a promise m of another thread  $\pi_2$  to a location  $L \in \mathcal{L}$ , we first execute  $\pi_2$  following its certification until it fulfills the promise m and then execute  $\pi_1$  following seq until it reads m. What makes this possible is Lemma 2 below. Using "reshuffling", (ii) is established as follows. Roughly speaking, ignoring the consistency requirement, for the first time a thread can read from a promise on a location in  $\mathcal{L}$ , we apply the above construction to get an  $\mathcal{L}$ -racy execution without reading any promise on  $\mathcal{L}$  (i.e., a  $\mathcal{L}$ -racy execution in the  $\mathcal{L}$ -PRF-machine), which contradicts the premise of (ii). (To meet the consistency requirement, the proof requires repeated applications of the reshuffling.)

**Lemma 2** (Promise Monotonicity). Let  $\langle \mathcal{T}, M \rangle$  be a (consistent) machine state with a promise m written by thread  $\pi_1$ . Suppose that  $\langle \mathcal{T}(\pi_2), M \rangle \to^* \xrightarrow{l} \langle T_2, \_ \rangle$  for some thread  $\pi_2 \neq \pi_1$ , label l, and thread state  $T_2$ . Then, there exist  $l_m \in \{\mathbb{W}(\mathtt{rlx}, m), \mathtt{RMW}(\_, \mathtt{rlx}, \_, m)\}$  and memory  $M_1$  such that:

•

$$\langle \mathcal{T}, M \rangle \xrightarrow{\pi_1, \underline{\ }}^* \xrightarrow{\pi_1, l_m} \langle \mathcal{T}[\pi_1 \mapsto \underline{\ }], M_1 \rangle$$

; and

•

$$\langle \mathcal{T}(\pi_2), M_1 \rangle \to^* \xrightarrow{l} \langle T_2, \_ \rangle$$

.

Remark 3. Promise consistency does not hold for PS and PS2 since RMW-store reordering breaks it. For global DRF-PF, a weaker property, which does hold for PS and PS2, suffices. Specifically, the above reshuffling may break during the execution of  $\pi_1$  following the sequence seq (before it reads m) only if  $\pi_1$  performs a racy RMW. Global DRF-PF follows from the race on the RMW, but not LDRF-PF since the location of the RMW may not be in  $\mathcal{L}$ .

#### 2.3.2 Local DRF-RA

To formulate LDRF-RA, we again start by defining a strengthening of PS2.1 w.r.t. a given set of locations.

**Definition 7.** Given a set  $\mathcal{L} \subseteq \mathsf{Loc}$ , the  $\mathcal{L}\text{-RA-machine}$  is the strengthening of the  $\mathcal{L}\text{-PF-machine}$  obtained by interpreting all accesses to  $\mathcal{L}$  as if they have release/acquire access modes (in (READ-HELPER) and (WRITE-HELPER)). We denote by  $[\![prog]\!]_{\mathrm{RA}}^{\mathcal{L}}$  the set of all behaviors of a program prog that are allowed by the  $\mathcal{L}\text{-RA-machine}$ .

Next, for stating the premise of LDRF-RA, we introduce the "RA-race-detecting-machine". For that we adopt a "happens-before-based" notion of race, where a necessary condition on the happens-before relation is expressed using the views of the promising semantics. Roughly speaking, the RA-race-detecting-machine invokes UB whenever the machine reaches a state where (i) some thread  $\pi$  is about to read from a location  $L \in \mathcal{L}$ ; (ii) there exists a message m in memory written by some write to L that does not "happen-before" the read (which corresponds to the fact that the view of  $\pi$  for L is strictly lower than the timestamp of m); and (iii) at least one of the write or the read is not annotated as a release/acquire access in the program. This is formalized as follows.

**Definition 8.** The  $\mathcal{L}$ -RA-race-detecting-machine is the machine obtained from the  $\mathcal{L}$ -RA-machine by adding following thread configuration step:

$$\begin{split} L \in \mathcal{L} & \quad \lambda \in \{ \mathsf{R}(o_{\mathsf{R}}, L, \_), \mathsf{RMW}(o_{\mathsf{R}}, \_, L, \_, \_) \} & \quad \sigma \xrightarrow{\lambda} \_ \\ & \quad V(L) < t & \quad m = \langle L \mathbf{0}_{\_}, \_, t \rangle_{\_} \in M \\ & \quad \underbrace{o_{\mathsf{R}} = \mathtt{rlx} \vee m \text{ was written by a non-release write}^9}_{\left\langle \left\langle \sigma, V, \_ \right\rangle, M \right\rangle \xrightarrow{\mathtt{race}} \left\langle \left\langle \bot, V, \emptyset \right\rangle, M \right\rangle} \end{split}$$

**Remark 4.** A similar view-based definition of a race can be also used in LDRF-PF. However, such definition would unnecessarily deem too many programs as racy, resulting in a weaker guarantee. For example, with a view-based definition of a race in LDRF-PF, we would not be able to show the absence of  $\{X,Y\}$ -PF-racy executions for the program in Example 8 (since there is no synchronization from the write to X in  $\pi_1$  to the read from X in  $\pi_3$ ).

<sup>&</sup>lt;sup>9</sup>Formally, this requires to record the writing access mode in messages.

LDRF-RA is formulated as follows.

**Theorem 3** (LDRF-RA). If the race transition is never enabled in runs of the  $\mathcal{L}$ -RA-race-detecting-machine on prog, then  $[prog]_{PS2,1} = [prog]_{RA}^{\mathcal{L}}$ .

**Remark 5.** When  $\mathcal{L} = \mathsf{Loc}$ , since the  $\mathcal{L}$ -RA-machine cannot make *any* promise, the race detecting step can be revised as follows (where  $\to$  is the thread step of the  $\mathcal{L}$ -RA-machine):

$$\begin{split} & \langle \langle \sigma, V, P \rangle, M \rangle \xrightarrow{l} \langle \langle \sigma', V', P' \rangle, M' \rangle & l \in \{ \mathsf{R}(o_\mathsf{R}, \langle L \mathsf{Q}_-, \_, \_ \rangle_-), \mathsf{RMW}(o_\mathsf{R}, \_, \langle L \mathsf{Q}_-, \_, \_ \rangle_-, \_) \} \\ & V(L) < t & m = \langle L \mathsf{Q}_-, \_, t \rangle_- \in M \\ & o_\mathsf{R} = \mathsf{rlx} \vee m \text{ was written by a non-release write} \\ & & \langle \langle \sigma, V, P \rangle, M \rangle \xrightarrow{\mathtt{race}} \langle \langle \sigma', V', P' \rangle, M' \rangle \end{split}$$

Then, the global DRF-RA guarantee follows from the local one. The "naive" LDRF-RA discussed in §2.2.2 (which cannot not hold together with all optimizations allowed in PS2.1) formally means to use the above step for race detection in the  $\mathcal{L}$ -RA-race-detecting-machine.

**Example 9.** The following example is a variant of the common "load-buffering" test. We show that, using LDRF-RA, this program never exhibits the a = 1 outcome.

Assuming RA semantics for X, both the writes to X and to Y cannot be promised, and clearly a=1 is not allowed. Now, we show that the race transition is never enabled in executions of this program in the  $\{X\}$ -RA-race-detecting-machine. Indeed, since the write to X in  $\pi_2$  can only be executed after the write to Y in  $\pi_1$  is executed (which cannot be promised because it is a release write), there cannot be any message to X except for the initial message before the read from X in  $\pi_1$  is executed.

We note that our race condition is strictly stronger (identifying fewer programs as racy) than the standard "happens-before"-based race notion. The latter would deem this program as  $\{X\}$ -racy. as there is no "happens-before" relation between the accesses to X (since the read of Y is relaxed).

**Example 10.** We apply LDRF-RA on a location with a write-write race. In the following program, the first two threads access X and Y and raise flags Z and W.

The third thread waits on both flags and then accesses X and Y.

$$\begin{array}{ll} a := X^{\mathtt{rlx}} \\ Y^{\mathtt{rlx}} := a + 2 \\ Z^{\mathtt{rel}} := 1 \end{array} \quad \begin{array}{ll} b := X^{\mathtt{rlx}} \\ Y^{\mathtt{rlx}} := b + 4 \\ W^{\mathtt{rel}} := 1 \end{array} \quad \begin{array}{ll} \mathbf{while}(Z^{\mathtt{acq}} + W^{\mathtt{acq}} < 2) \ \mathbf{do} \\ \mathbf{skip} \\ X^{\mathtt{rlx}} := 1 \\ c := Y^{\mathtt{rlx}} \ \ \#2 \ or \ 4 \end{array}$$

While there is a write-write race on Y, there is no write-read race on X and Y, and so the race transition is never enabled in executions of this program in the  $\{X,Y\}$ -RA-race-detecting-machine. LDRF-RA ensures that it is safe to assume RA semantics for X and Y. Then, knowing only RA semantics, it follows that  $c \in \{2,4\}$  holds when this program terminates.

**Remark 6.** To simplify the presentation, we did not discuss release/acquire fences. These allow fine-grained control on the required synchronization, which can improve performance, but results in more races involving relaxed accesses. For the purpose of reasoning about fences using LDRF, we observe that the following transformations do not affect the possible behaviors in the promising semantics:

$$\begin{array}{llll} r_1 := X^{\mathtt{rlx}} & r_1 := X^{\mathtt{acq}} \\ \vdots & \vdots & \vdots \\ r_n := X^{\mathtt{rlx}} & r_n := X^{\mathtt{acq}} \\ \mathtt{fence}^{\mathtt{acq}} & \mathtt{fence}^{\mathtt{acq}} \end{array} \qquad \begin{array}{ll} \mathtt{fence}^{\mathtt{rel}} & \mathtt{fence}^{\mathtt{rel}} \\ X_0^{\mathtt{rlx}} := r_0 & X_0^{\mathtt{rel}} := r_0 \\ X_1^{\mathtt{rlx}} := r_1 & \leftrightsquigarrow & X_1^{\mathtt{srlx}} := r_1 \\ \vdots & \vdots & \vdots \\ X_n^{\mathtt{rlx}} := r_n & X_n^{\mathtt{srlx}} := r_n \end{array}$$

Programmers may safely use the (better performant) left-hand sides in programs, while assuming the (stronger) semantics provided by the right-hand sides (also for establishing the premise of the LDRF theorem).

#### 2.3.3 Local DRF-SC

The final LDRF guarantee, LDRF-SC, provides the strongest semantics for non-racy accesses, but also requires much more for accesses to be considered non-racy. We note that, unlike C/C++11 [27, 28, 13], the promising semantics does not provide sequentially consistent accesses (it only has SC fences). Thus, a *global* DRF-SC can only pointlessly ensure SC semantics for programs that have no races whatsoever (with no mechanism to actually avoid races). Nevertheless, *local* DRF-SC is still meaningful as it only requires to avoid races on certain locations.

As before, we first define the stronger semantics and the notion of a race.

**Definition 9.** In the context of a machine state, we call a message maximal if there does not exist a message with the same location and higher timestamp. For  $\mathcal{L} \subseteq \mathsf{Loc}$ , the  $\mathcal{L}\text{-}SC\text{-}machine}$  is the strengthening of the  $\mathcal{L}\text{-}RA\text{-}machine}$  obtained by requiring that for every  $L \in \mathcal{L}$ :

- reads from L read from maximal messages; and

- $\bullet$  writes to L write maximal messages.

We denote by  $[prog]_{SC}^{\mathcal{L}}$  the set of all behaviors of a program prog that are allowed by the  $\mathcal{L}$ -SC-machine.

To state the premise of LDRF-SC, we introduce the "SC-race-detecting-machine". It is defined as the RA-race-detecting-machine, except that races may also occur (i) between two RA accesses, and (ii) between two writes.

**Definition 10.** The  $\mathcal{L}$ -SC-race-detecting-machine is the machine obtained from the  $\mathcal{L}$ -SC-machine by adding following thread step:

$$\begin{array}{ccc} L \in \mathcal{L} & \lambda \in \{\mathtt{R}(\_,L,\_), \mathtt{W}(\_,L,\_), \mathtt{RMW}(\_,\_,L,\_,\_)\} & \sigma \xrightarrow{\lambda} \_ \\ & & V(L) < t & m = \langle L \mathtt{Q}_\_,\_,t \rangle_- \in M \\ & & & \langle \langle \sigma, V,\_ \rangle, M \rangle \xrightarrow{\mathtt{race}} \langle \langle \bot, V, \emptyset \rangle, M \rangle \end{array}$$

Then, LDRF-SC is formulated as follows.

**Theorem 4** (LDRF-SC). If the race transition is never enabled in runs of the  $\mathcal{L}$ -SC-race-detecting-machine on prog, then  $[\![prog]\!]_{PS2.1}^{\mathcal{L}} = [\![prog]\!]_{SC}^{\mathcal{L}}$ .

**Example 11.** Consider the message passing program:

$$D^{\text{rlx}} := 42$$

$$F^{\text{rel}} := 1$$

$$a := F^{\text{acq}}$$

$$if a = 1 \text{ then}$$

$$a := D^{\text{rlx}} \#42$$

(MP)

In all its executions in the  $\{D\}$ -SC-race-detecting-machine, the view of  $\pi_2$  for D after reading 1 from F points to the message D=42 written by  $\pi_1$ . Therefore, the race transition is never enabled for this program in the  $\{D\}$ -SC-race-detecting-machine. Then, LDRF-SC with  $\mathcal{L}=\{D\}$  ensures SC semantics on the location D.

#### 2.3.4 Time-wise Local DRF Guarantees

In this subsection, we demonstrate generalized LDRF guarantees, namely "time-wise LDRF guarantees." Specifically, we provide two theorems, time-wise LDRF-PF (LDRF-PF-Time) and time-wise LDRF-SC (LDRF-SC-Time). Roughly speaking, time-wise LDRF guarantees say that, given a machine state  $\Sigma$ , the next possible machine steps in PS are equivalent to those in certain stronger semantics provided that  $\Sigma$  is not a racy state in the stronger semantics. Since these guarantees are applied to a machine state instead of the full execution of a program, they do not require race-freedom of the machine steps taken before reaching the given machine state. Moreover, starting from a given machine state, one can assume a stronger semantics until it reaches a racy machine state.

It is important to note that unlike Thm. 4 where the SC semantics denotes a strengthening of RA accessing only the latest messages to each location, the SC semantics of LDRF-SC-Time is not RA-synchronizing, *i.e.*, it is a strengthening of PF accessing only the latest messages to each location. Indeed, this is very similar to the local SC semantics of LDRF of [18]. Though we have another formulation of time-wise LDRF-SC with the SC semantics accompanying RA synchronization, which we believe is provable, we do not present it as the theorem is too complicated due to the presence of RA synchronizations. For the same reason, we do not present the "time-wise LDRF-RA" theorem as well.

To formulate LDRF-PF-Time, we first define an  $\mathcal{L}$ -racy machine state. Roughly, a machine state  $\Sigma$  is  $\mathcal{L}$ -racy if (i) starting from  $\Sigma$ , a thread can take multiple steps and write a message m to a location in  $\mathcal{L}$  by a relaxed write; and (ii) immediately after m is written, another thread can take multiple steps and read the message m.

**Definition 11.** Given a set  $\mathcal{L} \subseteq \mathsf{Loc}$ , a machine state  $\Sigma = \langle \mathcal{T}, M \rangle$  is  $\mathcal{L}$ -racy if there exist a location  $X \in \mathcal{L}$ , two different threads  $\pi_1 \neq \pi_2$ , a memory M', labels  $l_1, l_2$ , and a message m such that:

- $\langle \mathcal{T}, M \rangle \xrightarrow{\pi_1, -} * \xrightarrow{\pi_1, l_1} \langle -, M_1 \rangle$

- $\langle \mathcal{T}(\pi_2), M_1 \rangle \to^* \xrightarrow{l_2} \langle_{-, -} \rangle$

- $l_1 \in \{ \mathbb{W}(\texttt{rlx}, m), \texttt{RMW}(\_, \texttt{rlx}, \_, m) \} \land l_2 \in \{ \mathbb{R}(\_, m), \mathbb{RMW}(\_, \_, m, \_) \}$

Using the above definition, LDRF-PF-Time is formulated as follows. The main difference of LDRF-PF-Time from LDRF-PF is that it does not consider racy steps taken before reaching  $\Sigma$ , to which LDRF-PF-Time applies. Moreover, one can stop applying LDRF-PF-Time whenever the machine reaches a racy state.

**Theorem 5** (LDRF-PF-Time). Given a set  $\mathcal{L} \subseteq \mathsf{Loc}$  and a machine state  $\langle \mathcal{T}, M \rangle$  which has no promise to locations in  $\mathcal{L}$ , if  $\langle \mathcal{T}, M \rangle$  has some execution in the PS2.1 with a final outcome R, then one of the following holds.

- $\langle \mathcal{T}, M \rangle$  has some execution in the  $\mathcal{L}$ -PF-machine with the outcome R.

- $\langle \mathcal{T}, M \rangle$  can reach a  $\mathcal{L}$ -racy state  $\langle \mathcal{T}', M' \rangle$  in the  $\mathcal{L}$ -PF-machine, and  $\langle \mathcal{T}', M' \rangle$  has some execution in the PS2.1 with the outcome R.

As we previously described, the SC semantics of LDRF-SC-Time varies from that of Thm. 4. Therefore, we first define the SC machine and the SC-race-detecting-machine of LDRF-SC-Time.